Intel Foundry Direct Connect 2025

Intel's foundry endeavor is starting to fall in place. A comparison with TSMC

Intel’s Foundry Direct Connect 2025 event was a bold attempt to reintroduce Intel as a serious foundry player. Packed with updates on advanced nodes and chiplet packaging, the event revealed how far Intel is willing to go to transform itself.

Tan Lip-Bu Sets the Tone

In his inaugural keynote as Intel's CEO, Tan Lip-Bu emphasized a customer-centric approach, urging partners to provide candid feedback to drive continuous improvement. Tan's message was clear that Intel is fully committed to its foundry business and is taking decisive steps to earn the trust of its customers.

More important today is to listen to our customer. I would love your feedback so that we can better serve you.

Now I've been the CEO for about 5 weeks now. And then some of the people are asking me, since I joined Intel, Lip-Bu, "are you committed to the foundry?" The answer is yes. I'm so excited today to share with you. I'm committed to make the Intel Foundry successful, and I know there are areas we need to improve. I'm determined to strengthen our road map and our partnership and our execution going forward. As we drive this improvement, we see a lot of opportunity ahead of us.

For once, we might have an Intel CEO who truly understands what it takes to succeed in the foundry business.

I really embrace the industry standard IP and EDA so that we can really help you and serve you better. And this is truly a service business, and that is built on the foundational principle of trust. And you have to be patient to earn your trust. And then we have to really driving some of the technology to make sure that the yield and performance and reliability meet your requirement.

We will be guided by the Voice of the Customer, all of you, and we'll act on your feedback. We are humble in that approach, as you can tell, because we know your success is matter the most than anything else. And we work every day to earn your trust.

Source: Intel

TSMC has always emphasized trust as a core value of the company given that trust is the bedrock of the foundry business. Unlike IDMs, foundries don’t sell end products. They sell reliability, confidentiality and execution. When companies like Apple and NVIDIA hand over their most sensitive chip designs to a foundry, they require assurance that TSMC would never compete with them and to deliver as promised. Integrity and trust go hand in hand.

Source: TSMC

Seeing Intel labels trust as a foundational principle is both refreshing and assuring. Trust is not about exaggerating your future technology roadmap potential, but to provide a reliable roadmap that customers can depend on to deliver their new products on time. Of course, Intel’s challenge is unique as it’s both a foundry and an IDM competitor. Whether customers believe Intel can replicate the trust TSMC earned over 30 years will be central to its foundry ambitions. Tan Lip-Bu also understands that foundry is a service business. The mindset change is important as foundry is much more than having superior technology.

In another sign of Tan Lip-Bu strong interpersonal relationship, CEOs of all 3 major EDA tools Sassine Ghazi (Synopsys), Anirudh Devgan (Cadence) and Mike Ellow (Siemens EDA) went on stage.

Intel shared that they had invested a total of $90 billion on property, plant, equipment and R&D. For comparison, TSMC had spent a total of $150 billion in the same period which is more than 50% higher than Intel. This year, Intel will spend a gross capex of $18 billion (net capex of $8 to $11 billion) while TSMC will spend a total capex of $38 to 42 billion. Leverage, lack of scale, low utilization rate and a core business under threat remain impediment as Intel embarks on this capital-intensive business. TSMC is expected to grow its revenue by more than 25% to $110 billion this year, while Intel’s revenue is expected to decline by mid-single digit to $50 billion.

Source: Intel

Intel Foundry Process Roadmap

The main highlight of the process roadmap is 18A, 18A-P, 14A and 14A-E

Source: Intel

Intel 18A Is Ramping

Intel’s 18A will be the 1st node to feature two key technology innovations in RibbonFET, Intel’s gate-all-around transistor architecture, and PowerVia, their take on backside power delivery. 18A will boast a density improvement of 30%, performance/watt improvement of 15% relative to Intel 3.

Back in 2021, Pat Gelsinger came out with the target to achieve 5 nodes in 4 years. Intel is on track to meet the goal as 18A is in risk production with volume ramp expected later this year. However, real volume ramp of Panther Lake (built on 18A) will be in 2026.

Defect density continues to improve in Q4 2024 and Q1 2025. Intel had previously revealed that their D0 (defect density) is 0.4 for 18A in September 2024. Intel’s D0 is likely to be somewhere between 0.2 to 0.3 right now. While this is higher than TSMC’s D0 of <0.2 for N2, Intel is on track for mass production of 18A.

Source: TSMC Technology Symposium 2025

Introduced during the event, Intel 18A-P is a newly announced enhancement of Intel’s 18A process node. Intel’s 18A-P is a performance-enhanced variant of 18A optimized for customers demanding better performance.

With mass production in 2026, 18A-P has design rule compatibility with 18A and offers an 8% improvement in performance. Because of the design rule compatibility, most of the IP will be able to port over from 18A to 18A-P seamlessly. Again, this is like what TSMC has always done in introducing application specific derivatives nodes that are more suitable for clients. Design rule is usually compatible between derivatives nodes. N3E was introduced at a lower cost to replace N3B and now TSMC offers N3X, N3A and N3C.

With the better performance and more mature IP, 18A-P will become more competitive in the foundry market.

Source: TSMC Technology Symposium 2025

Another variant, 18A-PT, has also been introduced with the main feature being the addition of TSV. This will be more suitable for AI applications where 18A-PT can be used as a base die for further integration with HBM.

Source: Intel

Intel 14A: High-NA EUV Adoption Remains Uncertain

Intel also commented on 14A which is set for risk production in Oregon in 2027. 14A is expected to offer a 15-20% improvement in performance/ watt, 30% density gain, and 25-35% power reduction compared to 18A. At the same time, 14A will feature their 2nd generation of RibbonFET and backside power delivery.

While some might claim that Intel is 1 year ahead of TSMC with 14A, 2028 is likely to be the year of mass production for 14A as 2027 is the year of risk production. We have seen how 18A has started risk production, but actual mass production tracks closely with TSMC.

Source: TSMC Technology Symposium 2025

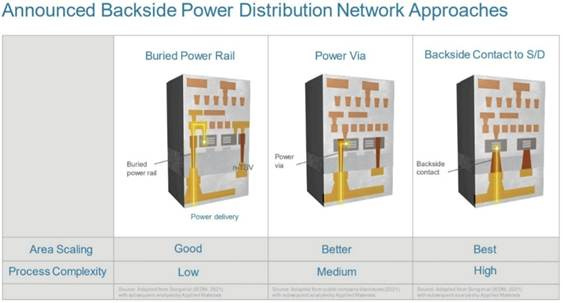

For the 2nd generation of backside power delivery, Intel has called it PowerDirect. PowerDirect is a more advanced form of backside power delivery network as it involves direct backside contact to the source/drain. This is like TSMC’s adoption of Super Power Rail for A16 in 2026. For 18A, Intel had adopted the Power Via method which is an intermediate solution between Buried Power Rail and Direct Contact.

Source: Applied Material

With regards to High-NA EUV, Intel made a comment that implies it is evaluating the cost effectiveness of introducing the new technology at 14A. Cost effectiveness is an important consideration for foundry. While High-NA EUV can reduce the number of process steps and simplify the process, the additional cost is still a hurdle for end customers. This is why I continue to believe that High-NA EUV adoption by TSMC will be more likely in 2030.

Intel’s roadmap still represents a few years delay in High-NA EUV adoption as Intel under Pat Gelsinger had previously mentioned about High-NA EUV involvement in production starting in 2025. Pat Gelsinger was too aggressive on being the 1st to High-NA EUV when we have seen previous multi-years delay for Low-NA EUV adoption. High-NA EUV alone is not going to help Intel wins the foundry market.

Source: ASML and Intel joint announcement

This is a change in tone regarding to the adoption of High-NA EUV for 14A. Regardless, customers can proceed with their 14A design as it does not matter whether High-NA EUV will be adopted or not.

One of the differentiating factors on 14A is High-NA EUV tool. In Oregon, we have landed our second High-NA EUV tool. In fact, this tool came up much faster compared to our first one, and we are working in great collaboration with ASML. The tool is performing well to its expectations. I want to make 2 points for the audience today.

The first one is Intel still has the option to have either a low-NA or a High-NA solution on our 14A technology, and it's design rule compatible. There will be no impact to the customers depending on the path that we choose.

Second, the High-NA EUV is performing to the expectations, and we will introduce it at the right time. We already have data on 18A as well as 14A that shows yield parity between our low-NA-based solution and a High-NA-based solution. So we are continuing to make progress on the technology front and ensuring that we have the right options available for us to make sure the solution we deliver to our customers has the lowest risk and the best reward in terms of the decisions we make.

Advanced Packaging

Intel EMIB (Embedded Multi-die Interconnect Bridge) is a 2.5D advanced packaging technology that enables high-bandwidth, low-latency communication between multiple chiplets on a single substrate. Instead of using silicon interposer like CoWoS, it uses silicon bridge to connect the dies.

Intel announced the introduction of TSV (Through-Silicon Vias) capability for their EMIB technology with the EMIB-T solution. This is a more scalable solution, especially if AI clients wanted to add more HBM content.

Source: Intel

The other key advanced packaging solution of Intel is Foveros. Intel has introduced 2 new solutions, Foveros-B and Foveros-R, that will be production ready in 2027.

Foveros-S uses silicon interposer and is in use for PC application

Foveros-R uses RDL (redistribution layer) as a cost sensitive solution

Foveros-B combines both RDL and silicon bridge for complex designs

Source: Intel

This is similar with TSMC’s 3 versions of CoWoS

CoWoS-S uses silicon interposer and is adopted by NVIDIA’s Hopper

CoWoS-R uses RDL (redistribution layer) as the interposer and is adopted by AWS’s Tranium

CoWoS-L uses an interposer with a Local Silicon Interconnect (LSI) chip for die-to-die interconnect and RDL layers for power and signal delivery. This is adopted by NVIDIA’s Blackwell

Source: TSMC

The next advancement will be Intel’s Foveros Direct, which is their 3D stacking solution. Through die-to-wafer hybrid bonding, dies are bonded to the substrate wafer using copper-to-copper interconnect. Bond pitch smaller than 10 um can be achieved as compared to sub-25 um for Foveros 2.5D.

Source: Intel

Advanced packaging is an area that Intel is obviously still lagging TSMC by a few years. While TSMC has started to implement CoWoS-L for NVIDIA’s Blackwell in 2024, Intel’s Foveros-B will only be ready in 2027. In the area of hybrid bonding, TSMC’s SoIC has been in production since 2022 with pitch size as small as 6um in 2025.

Source: TSMC

Strengthening the Ecosystem

Intel also announced the formation of the Intel Foundry Chiplet Alliance and Value Chain Alliance, aiming to foster collaboration across the semiconductor ecosystem. Key EDA partners like Synopsys, Cadence and Siemens are working closely with Intel to develop certified design flows and IP for the 18A and 14A nodes. These collaborations are essential for ensuring a robust design environment for customers.

Source: Intel

It’s a smart move as Intel knows it can’t go it alone. And it’s borrowing a page from TSMC’s playbook by trying to create a collaborative ecosystem that makes it easier for customers to bring designs to tape-out. There is still lots for Intel to do to catch up with TSMC’s well known Open Innovation Platform.

Source: TSMC

Conclusion

If former CEO Pat Gelsinger was focused on getting Intel technologically ready for the foundry race, Tan Lip-Bu is now mastering the intricacies of the foundry business. Intel’s new CEO understands what it takes to succeed as a foundry and he’s beginning to speak the language of TSMC. Intel Foundry is emerging as a player to watch in the semiconductor foundry industry, even if it still faces clear disadvantages across several fronts.

You can also check out my recent article on TSMC 2025 Technology Symposium.